競賽得獎團隊簡介

[年度競賽獲獎論文及作品發表]

2017年8月4日(五)10:00~11:30

墾丁福華渡假飯店1樓M103

[Analog & RF]

主持人:張順志教授 (成功大學電機系)

講題:高效能連續時間三角積分調變器之設計

主講人:翁展翔 (聯發科技 資深工程師)

獲獎紀錄:TICD博碩士論文獎

Biography

2001~2005 國立中央大學電機系

2005~2008 國立台灣大學電子工程研究所碩士

2008~2011 絡達科技 類比設計工程師

2011~2015 國立台灣大學電子工程研究所博士

2015~至今 聯發科技 資深工程師

Abstract

演講主題以開發高效能連續時間三角積分調變器為主軸,以低功耗、縮小晶片面積及提高解析度為設計目標,開發出許多技術,適合應用於通訊系統中的連續時間三角積分調變器、智慧型溫度感測器(具有感測前端的數位類比轉換器之通稱),以及經常使用低功耗類比數位轉換器的IoT(internet of thing)應用中。本演講希望透過淺顯易懂的方式,傳達在設計連續時間調變器的過程當中,所面臨設計上的挑戰,以及如何透過所提出技術的,來解決當前的問題,並達到一個低功率消耗、高效能的調變器設計。

[Analog & RF]

DA-1 一個利用殘值超取樣架構的十二位元每秒取樣四千萬次的連續漸進逼近式類比數位轉換器

A 12-Bit 40-MS/s Successive-approximation Analog-to-digital Converters with Residue Oversampling Techniques

隊員:許中瑋、張力仁、孔致遠、曾華安 / 國立成功大學 電機工程學系

指導教授:張順志教授 / 成功大學電機系

得獎紀錄:2016旺宏金矽獎 / 設計組評審團鑽石大賞

作品簡介:

本作品提出一個可以應用於高解析度類比數位轉換器的殘值超取樣技術。此技術利用不同電容陣列排列方法來產生不同的電壓殘值,接著再利用這些殘值解析出一個較精確的數位碼。簡而言之,此技巧結合了動態元件匹配( Dynamic Element Matching )與超取樣( Oversampling )兩種技術的概念,其消耗少量的時間與能量即可有效降低電容因製程造成的不匹配與晶片內部雜訊的影響。利用本作品所提出的技巧所研製之雛型晶片,可以不需要經過複雜的校正電路即可增加類比數位轉換器的精確度。

[Analog & RF]

DA-2 應用快速收斂技術之兩百億位元可適性線性等化器

隊員:陳冠宇、陳先哲 / 國立臺灣大學 電子工程學研究所

指導教授:劉深淵教授 / 國立臺灣大學 電子工程學研究所

得獎紀錄:

2016 第十六屆旺宏金矽獎 設計組 評審團金獎

作品簡介:

生活中,我們對於有線通訊系統速度的要求越來越高,如此可縮短資料傳輸的時間,便利我們的生活。然而,高速傳輸的系統將會面臨資料失真、錯誤等難題,因此,需要置入等化器(Equalizer)以還原真實的資料,對於資料傳遞的通道也須具備有適應性(Adaptive) 。我們的研究即是在低功率消耗的前提下,開發一個使等化器快速適應資料傳遞通道的演算法,而研究成果顯示不到3微秒的時間內即可達成此一目標。

[Analog & RF]

DA-3 利用單電感多浮動輸出轉換器實現之高效率及高色彩解析度發光二極體驅動電路

Single-inductor Multiple-floating-output Converter for Realizing High Efficiency and High Color Resolution LED Driver

隊員:楊文豪、陳昕、林莉琪、林晏霆 / 國立交通大學 電子工程學研究所

指導教授:陳科宏教授 / 國立臺灣大學 電機工程學系

得獎紀錄:

2016旺宏金矽獎 設計組評審團銀獎

作品簡介:

近年來,電子產品皆朝向體積縮小化與降低成本之趨勢,故在設計電源管理晶片時,小體積且高效率即成為重要之考量。這使得單電感多輸出(Single-inductor multiple-output, SIMO)轉換器之架構被廣泛地應用於電子產品之電源管理晶片中。

而傳統架構中的單電感多輸出發光二極體(Light-Emitting Diode, LED)驅動電路,對於每組發光二極體調光(Dimming)之規格較受限制,由於無法達到每組輸出同時調光之功能,故往往導致(1)低色彩解析度與(2)閃爍(Flicker)之影響,其中閃爍將對人體造成不適,例如:頭痛、癲癇發作等。

本次作品之研究動機在於改良傳統架構中的單電感多輸出發光二極體驅動電路,藉由本專題所提出之單電感多浮動輸出(Single-inductor multiple-floating-output, SIMFO)架構,將各組輸出之開關從傳統串聯於其輸出端之方式改為並聯於其輸出端上,使得此驅動電路能達到同時調光之功能,故其色彩解析度將大幅提升,並能同時解決閃爍之問題,以避免其所造成對人體不適之影響。

[Digital/EDA/Poster Session]

2017年8月4日(五)10:00~11:30

墾丁福華渡假飯店1樓福華廳(II)

主持人:陳冠宏教授 (逢甲大學電子系)

[Digital & System]

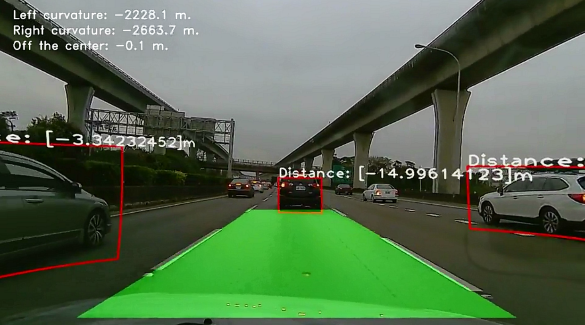

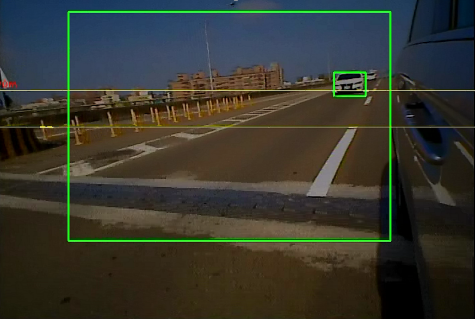

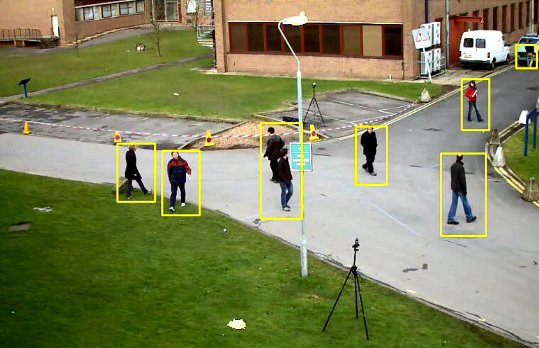

DA-4 深度學習嵌入式物件偵測技術

隊員:倪堉書、王兆以、曾建霖 / 逢甲大學 電子工程學系

指導教授:陳冠宏教授 / 逢甲大學 電子工學系

得獎紀錄:

2016旺宏金矽獎 應用組銀獎

作品簡介:

技術特點:

- 具高度適應能力的機器學習/深度學習方法

- 結合2D影像與3D立體視覺技術

- 精準的相機模型

- 多重物件偵測

- 精確的物件距離估算

- 地名路牌偵測與辨識技術

- 嵌入式智慧視覺運算能力

應用領域:

- 前瞻車用ADAS系統:前方防碰撞(FCWS)、盲區警示(BSD)系統、地名路牌偵測與辨識技術

- 智慧無人機/智慧自動駕駛車

- 定點智能監控系統:可疑人、物偵測、人流計算

車輛偵測、車道偏移偵測與測距 |

盲區警示(BSD)系統 |

定點智能監控系統 |

路牌偵測與辨識系統 |

[Digital & System]

DA-5 應用於穿戴式之即時車牌數字偵測系統

隊員:王彥珽、方志軒 / 國立中興大學 電機工程學系

指導教授:吳崇賓教授、范志鵬教授 / 國立中興大學 電機工程學系

得獎紀錄:

IED 2016智慧電子應用設計競賽,創意概念組-車用與運輸應用-銀獎

2017高階應用處理器AP聯盟「第二屆系統黑客松」-ARMmbed平台組-季軍

作品簡介:

即時功能之穿戴式車牌及數字辨識系統:配置兩個攝影機於眼鏡左側,對內攝影機為具有紅外線功能之SMI,對外攝影機為Logitech C920,為了避免使用者頭部大小不一配戴眼動儀裝置時滑落,於眼鏡掛勾後側加裝鬆緊帶,讓不同使用者可以個人舒適習慣調整。

本技術使用的眼動儀,其解析度皆為6401480,取像頻率每秒為30張影像,其對內攝影機以5~10分公的距離針對眼睛取像,拍攝角度由下往上仰角約為45度。此外,本系統已具備初步車牌辨識功能, 未來具有潛力可再進行多種字形辨識功能的擴增,以及穩定度之提高

[EDA]

DA-6 iTimerM 2.0

隊員:李培瑜 / 國立交通大學 電子工程學系

指導教授:江蕙如教授 / 國立交通大學 電子工程學系

得獎紀錄:

ACM TAU 2017 Macro Model Timing Contest / First Place Award

作品簡介:

The increase in the size of modern chip designs is forcing a paradigm shift from a traditional "flat timing" model to a "hierarchical timing" model. In the new paradigm, designs may be hierarchically partitioned into sub-blocks (or macros) that are timed in isolation (out-of-context), followed by a generation of a simplified timing macro-model that is plugged at the parent level of hierarchy. This additionally enables reuse of macros and a parallel chip design and optimization environment.

iTimerM 2.0, the first place winner of TAU 2017 contest, generates a compact and accurate timing macro model for enabling hierarchical timing analysis. The main idea is to separate the interface logic into variant and constant timing regions. Then, the variant timing region is reserved for accuracy, while the constant timing region is reduced for compactness. Compared with two common models used in industry, extracted timing model and interface logic model, our model has higher model accuracy and smaller model size.

[EDA ]

DA-7 Clock-Aware Placement for Large-Scale Heterogeneous FPGAs

隊員:郭玧質、黃朝琴、陳士鈞、蔣君涵 / 國立臺灣大學 電子工程學研究所

指導教授:張耀文教授 / 國立臺灣大學 電子工程學研究所

郭斯彥教授 / 國立臺灣大學 電機工程學系

得獎紀錄:2nd Place on 2017 ACM International Symposium on Physical Design (ISPD) Clock-Aware FPGA Placement Contest

作品簡介:

A modern FPGA often contains an ASIC-like clocking architecture which is crucial to achieve better skew and performance. Existing conventional FPGA placement algorithms seldom consider the clocking resource, and thus may lead to clock routing failures. To address the special FPGA clocking architecture, our work presents a novel clock-aware placement algorithm for large-scale heterogeneous FPGAs. Our algorithm consists of three stages: (1) a nonlinear global placement framework with clock fence region construction, (2) a clock-aware packing scheme, and (3) clock-aware legalization and detailed placement algorithms.

[EDA]

DA-8 Identical Fault Search

隊員:王登甲、劉晉亨、吉德軒 / 國立清華大學 資訊工程學系、張晏萍 / 國立清華大學 資訊系統與應用研究所

指導教授:王俊堯教授 / 國立清華大學 資訊工程學系

得獎紀錄:2016 CAD Contest @ ICCAD 國際賽定題組 亞軍

作品簡介:

電路設計的流程中,測試(testing)是必要的階段,需要驗證功能性是否正確,所以我們主要的目的是快速判斷哪些線路故障(fault)狀況會對電路造成相同影響。如果想要只利用電路模擬(simulation)測試所有線路是否正常,是非常耗時耗力且不實際的方法。因此,我們的方法是利用快速模擬及故障解析(fault collapsing),進行初步篩選及分類。接著,我們利用強制性賦值(mandatory assignment),推導及分析線路故障所造成的影響並完成分類。